Parallel Input Serial Output Shift Register Verilog Code

- Parallel Input Serial Output Shift Registers

- Parallel Input Serial Output Shift Register Verilog Code

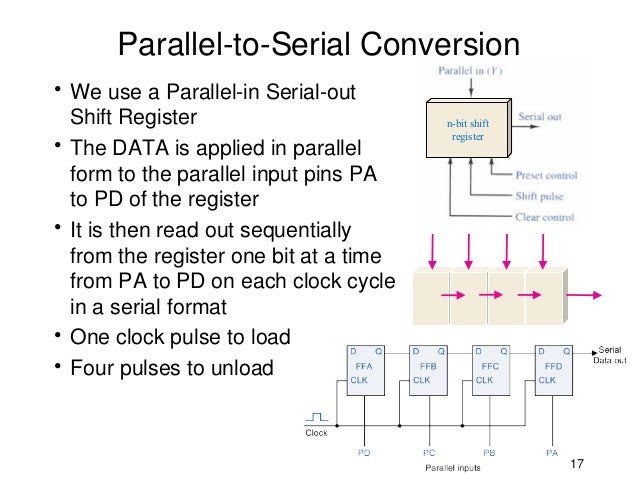

This sequential device loads the data present on its inputs and then moves or “shifts” it to its output once every clock cycle, hence the name Shift Register.

- Shift_reg is a 16-bit parallel output. I haven't shown any code for shift or for determining you've shifted 16-bits of data and now have your parallel output.

- Verilog code. Saturday, 4 July 2015. Shift register. Serial in serial out.

Hello I am trying to implement a parallel in serial out shift register based on the data sheet for the 74LV165A 8 bit parallel in serial out shift register

the spec sheet may be found at datasheet for 74LV165A

If I make my test bench begin by shifting in serially, then try to latch data on the parallel input the data does not appear. If I begin the test bench in with parallel latch enabled then the data appears on the Q and will clock through once shifting is enabled.

My goal is to shift several sets of data through this register however currently this behavior is preventing this. Any help would be very very appreciated, event if its just a hint :)

Currently I am monitoring the set and reset information and the Q lines.

Parallel Input Serial Output Shift Registers

1 Answer

$begingroup$Astute graphics plugins. You have misinterpreted the schematic. This line: Belajar membaca cepat.

O caso dos denunciantes invejosos pdf completo. nand3 control(!CP, !CE, PL, bus[16]);

is in contradiction with:

CPis active high,CEis active low (note the bar above the 'CE' on the schematic).- yet you use two inverted signals in the instantiation,

Also:

- the

busyou think a bus is just a wire (note the connecting dots!) - and I don't understand the

control_muxconcept entirely..

Parallel Input Serial Output Shift Register Verilog Code

Now, checking out the NXP documentation, the schematic of theirs differs from what you attached.

And finally, why are you hand-instantiating gates instead of just coding up the functionality?

Like:

After all, this is just a shift register with parallel async load.